# THERMAL TEST CHIPS TTC-1001A

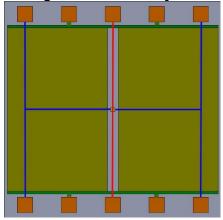

(1mm X 1mm Unit Cell) Wire Bond or Flip Chip

## **DESCRIPTION**

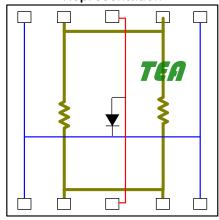

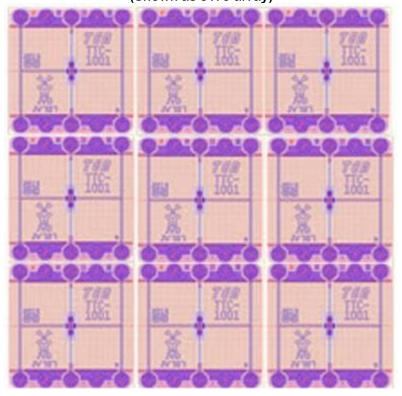

The TTC-1001 thermal test chip is designed to provide a maximum of flexibility for thermal characterization of semiconductor packages. Each Unit Cell can be used individually or in a square or rectangular array. A diode sensor for temperature measurements is in the center of the Unit Cell layout. This diode, when in arrayed cell configuration, can be individually addressed, allowing for temperature contour measurements across an array. The heating resistor in each cell of an array can be powered individually or wired in a series or parallel configuration for operation from a single power supply. In an array configuration, there are several resistor series strings that can be individually powered from separate power supplies or paralleled for operation from a single supply. The multiple cell array design allows for thermal measurements with non-uniform heating across the array.

#### **FEATURES**

- Proven silicon technology

- Format: bumped/flip chip or wire bond wafers or arrays of Unit Cells

- Kelvin connections to heating resistors for improved measurement accuracy

- Array form factor: may be arrayed square or rectangular

- Wire bond: on-chip adjacent cell interconnections of resistors and sensors providing for parallel or series or parallel/series resistor connections with peripheral pad wire bonding

- Bumped: all resistors and sensors may be individually connected

- One each resistor and sensor per Unit Cell; many resistors and sensors in arrays

- Uniform and non-uniform heating and planar temperature contours capable

- Suitable for both steady-state and transient thermal measurements

### **Contact TEA for:**

- ► Re-Distribution Layer (RDL) options

- ▶ Bump material composition options, including copper pillars

- ▶ Backside metal and thinning/polishing options

#### **SPECIFICATIONS**

| Electrical - Heating                                          | TTC-1001                                                                  |

|---------------------------------------------------------------|---------------------------------------------------------------------------|

| # of Resistors                                                | 1 (see Figure 2)                                                          |

| Resistance Value                                              | 10.5 Ω ±10 %                                                              |

| Resistance Variation                                          | ±10 % (for die from a specific wafer)                                     |

| Heating Resistor Power Dissipation for T <sub>J</sub> ≤ 150°C | 6.7W (~8.4V @ ~0.8A) max for 1ms<br>5.15W (~7.4V @ ~0.7A) max continuous  |

| Power Density (per Cell) for T <sub>J</sub> ≤ 150°C           | 588 W/cm <sup>2</sup> max for 1ms<br>453 W/cm <sup>2</sup> max continuous |

| Connection                                                    | Force & Sense wire bond or bump pads                                      |

| Resistor Coverage                                             | >69% of die area within wire bond or bump pads                            |

over, please

**SPECIFICATIONS** (continued)

|                                                  | 31 ECITICATIONS (CONTINUES)                                  |

|--------------------------------------------------|--------------------------------------------------------------|

| Electrical - Sensing                             | TTC-1001                                                     |

| # of Diodes                                      | 1 center                                                     |

| Nominal V <sub>F</sub>                           | 0.74V @ I <sub>F</sub> = 1 mA each diode                     |

| Nominal BV <sub>R</sub>                          | 5V @ $I_R = 10 \mu A$ each diode                             |

| Addressing                                       | Row and Column wire bond or bump pads                        |

| Physical                                         |                                                              |

| Wafer Size                                       | 200 mm (8 inch) Diameter Nominal                             |

| Unit Cell Size                                   | 1.00 x 1.00 mm (0.0394 X 0.0394 inch)                        |

| Die Layout                                       | See Figure 1                                                 |

| Array Capability                                 | See Figure 3                                                 |

| Wafer Thickness                                  | 725µm (0.029 inch) Nominal (thinning optional)               |

| Scribe Line Width Between Cells                  | 76µm                                                         |

| Wafer Backside Finish                            | Ground, un-polished (polishing optional)                     |

| Wafer Yield                                      | Greater than 80% (Center 127X127mm (5"x5") square area only) |

| Approximate Unit Cells/Wafer                     | >16,000 in center area                                       |

| Wire Bond Pad Size                               | 100μm (0.00394 inch) diameter                                |

| Wire Bond Pad Material                           | Al-Si(1.0%)-Cu(0.5%)                                         |

| Bump Material (other types optionally available) | Copper Pillar                                                |

| Bump Size (other sizes optionally available)     | ~90µm diameter, ~50µm height + ~20µm solder cap              |

Figure 2 Unit Cell Schematic Representation

Figure 3 Typical Array Layout (Shown as 3 X 3 array)

For assistance in electrical connection of Unit Cells in an array configuration, please contact TEA with your specific array requirements.

Descriptions in this document are for reference purposes only. Users are encouraged to perform their own inspection, testing and measurements, upon receipt of TEA product(s), for the parameters that are important for their application. TEA makes no warranty of any kind and will not be responsible for any consequential expenses associated with the customer's use of TEA's product(s).